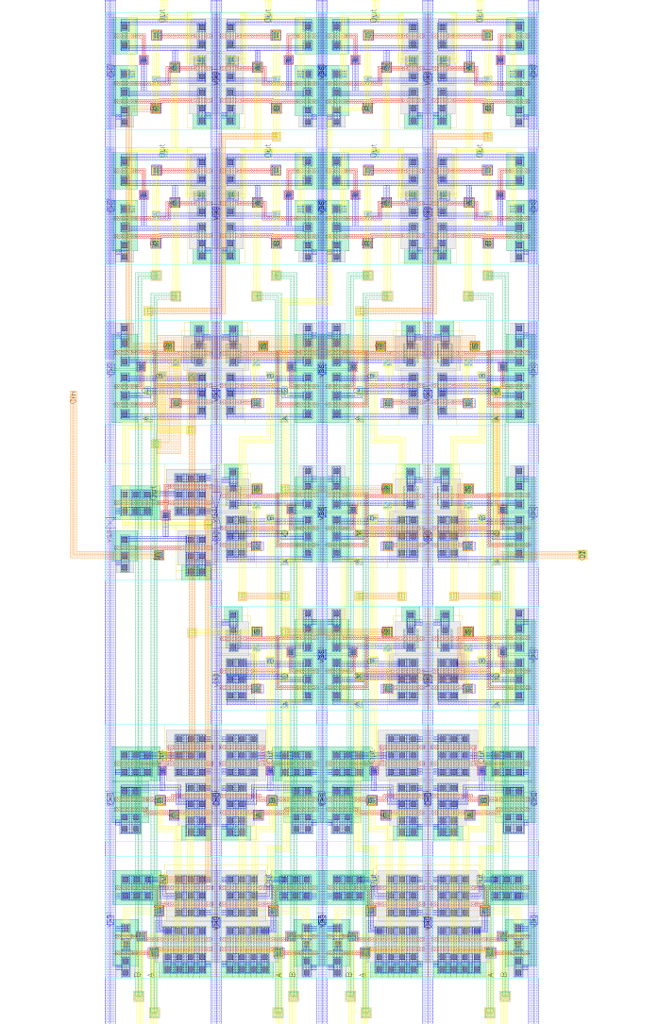

4-bit CMOS Transmission Gate Conditional Carry Select Adder

Course: ECE 637

Professor: Dr. Elmasry

Term: Winter 2003

A 4-bit Conditional Carry Select Adder module was designed and simulated using Cadence tools. A CMOS Transmission Gate logic style was used to form the multiplexers and XOR gates. The layout was done in Cadence using 0.18 µm technology from CMC, and was very compact and achieved a low-area of 802 µm2. In the 4-bit adder module, a worst-case delay of 50 ns was obtained. Our adder style scales very well to increasing word sizes. A 16-bit adder had a delay of only 1.10 ns and a 32-bit adder had a delay of 1.22 ns. The power is low due to the static design, at 200 µW for the 32-bit adder.

| Attachment | Size |

|---|---|

| 2.01 MB | |

| 478.22 KB |

Topic:

- 40455 reads

Add new comment